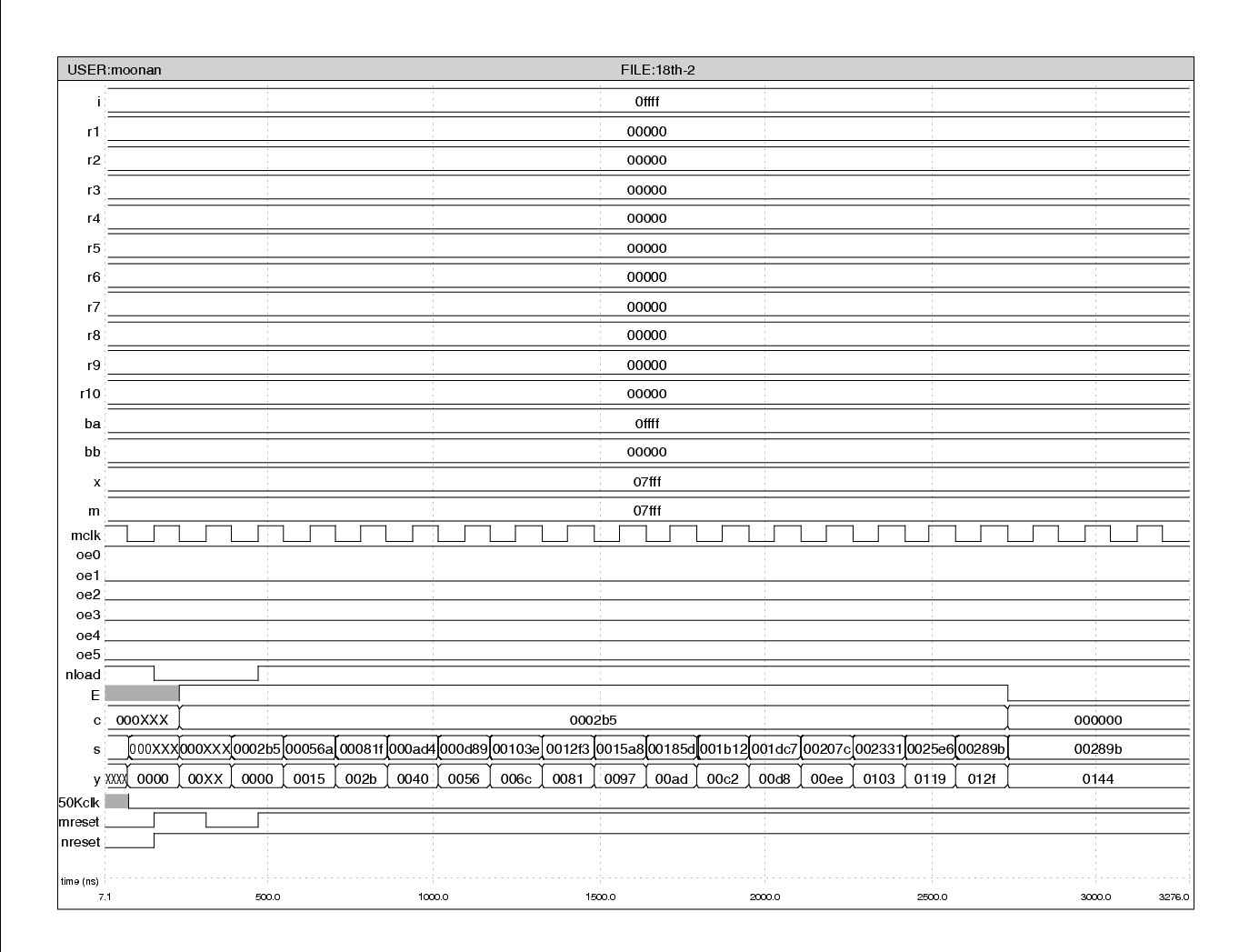

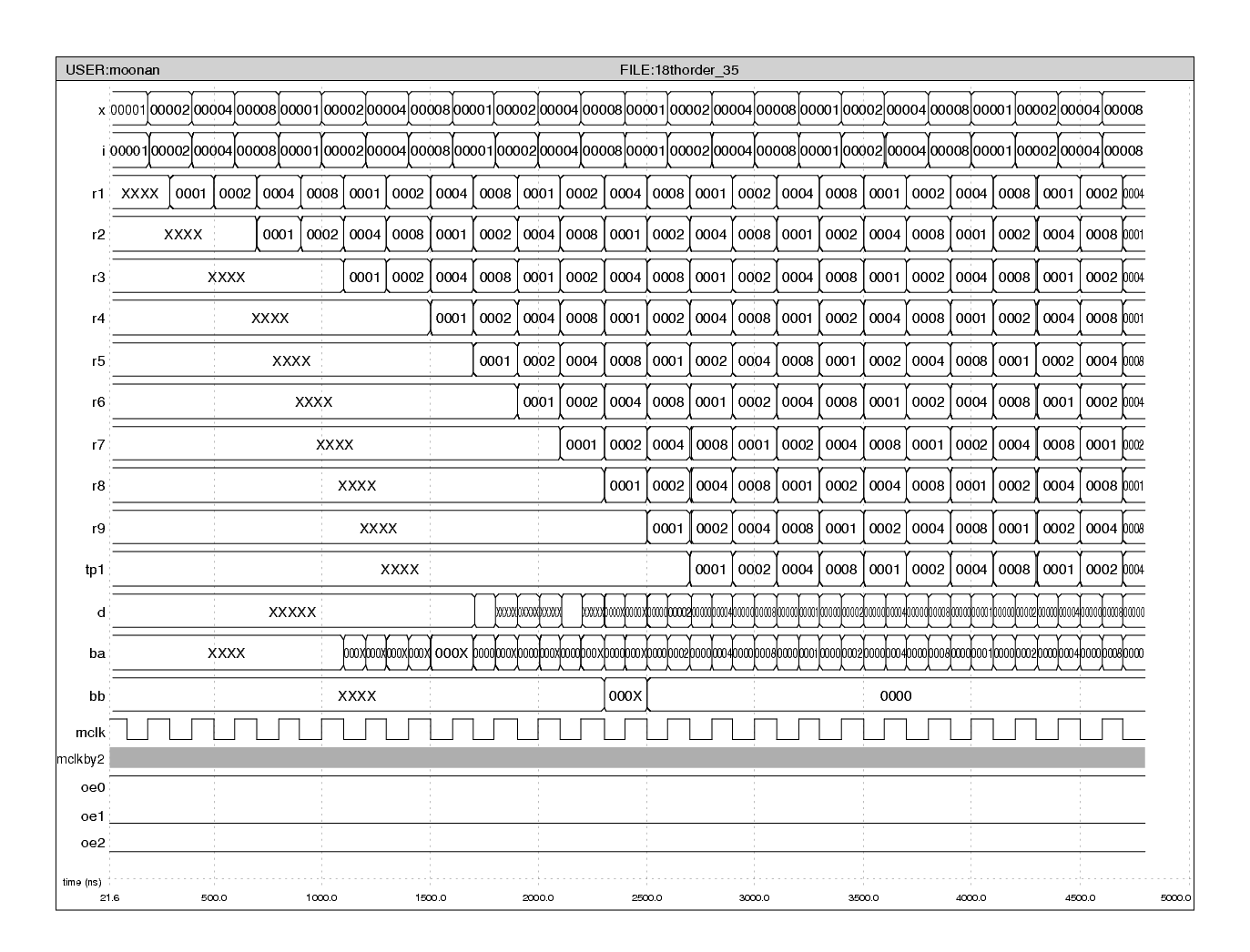

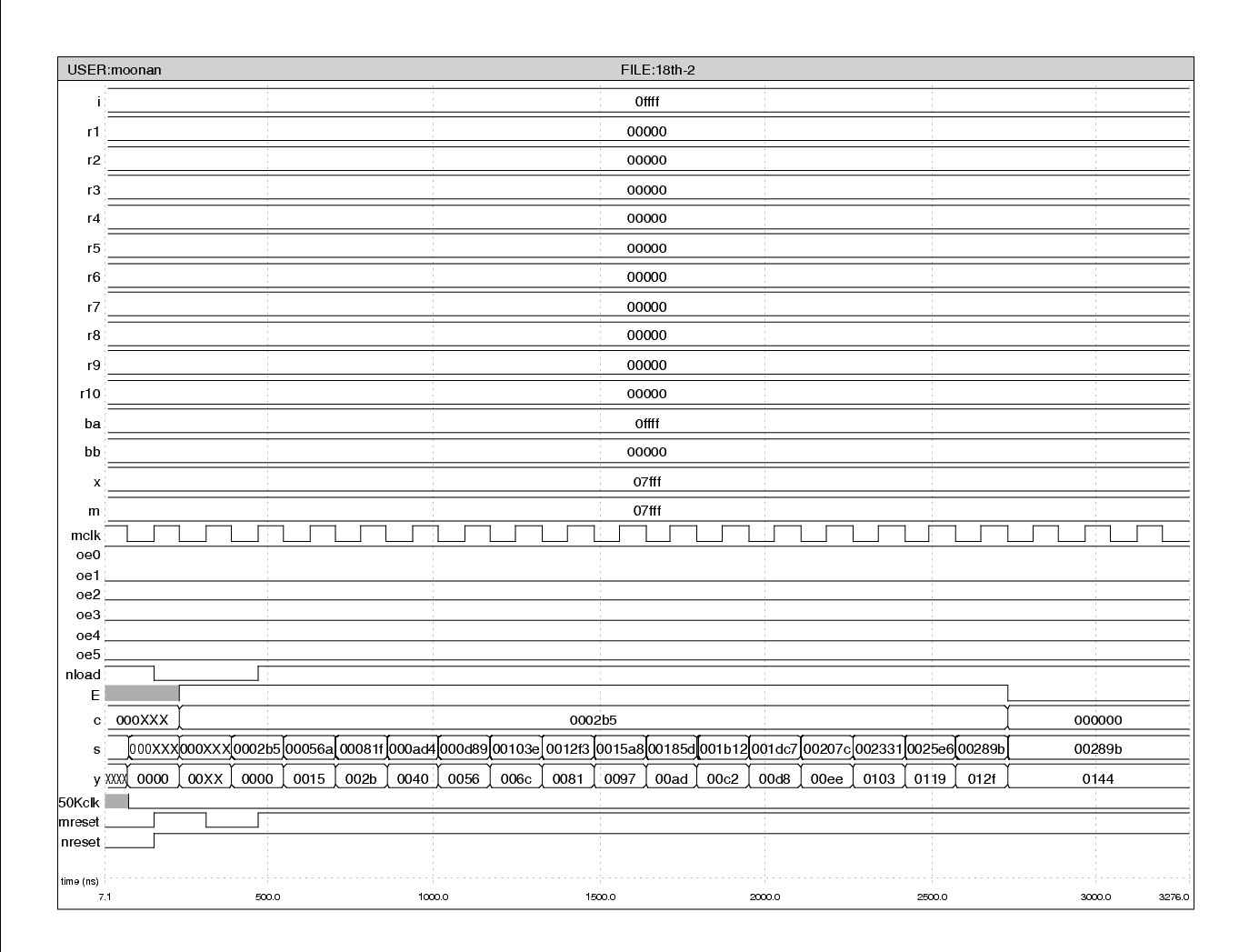

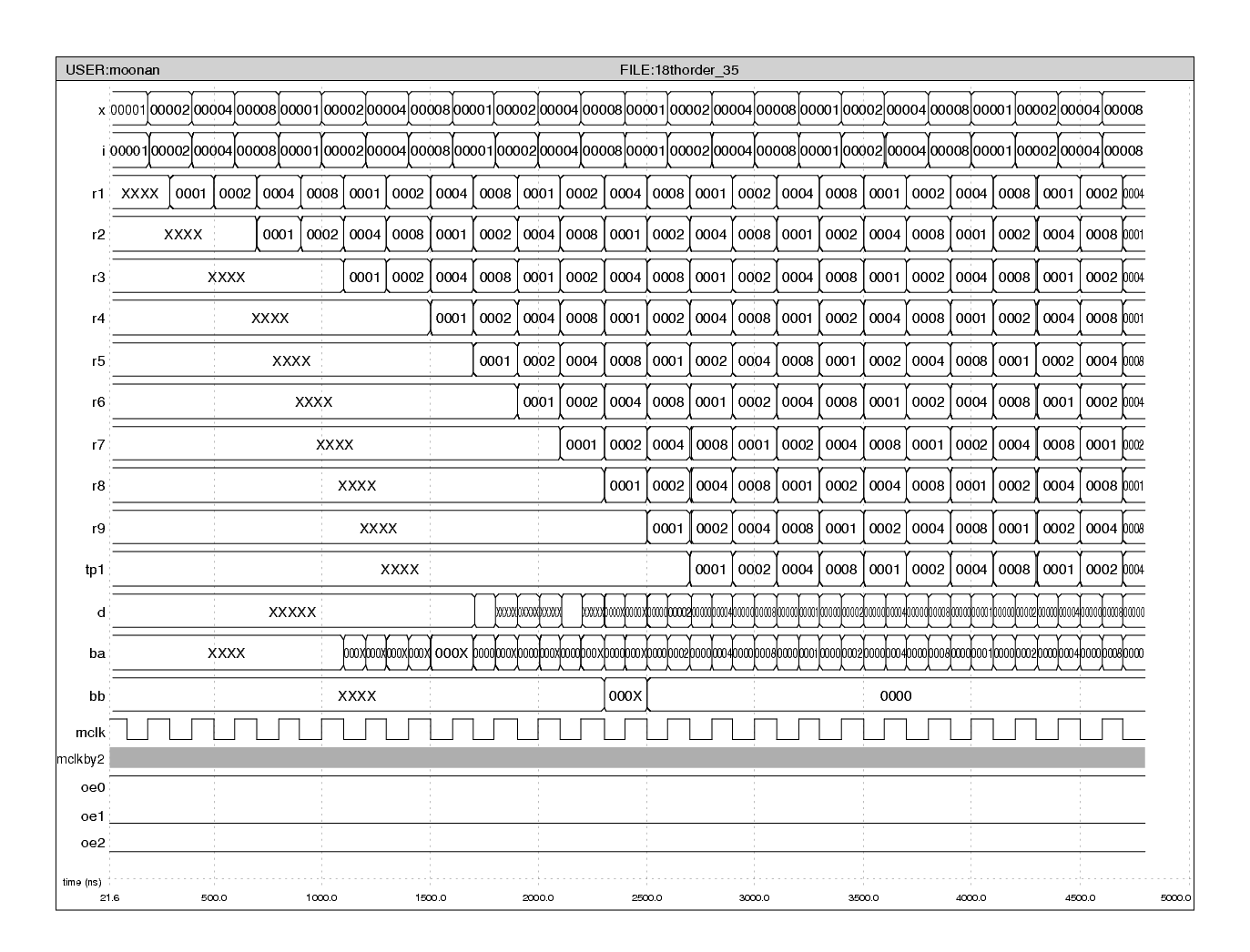

Sub-Cell Block Diagram, Placement, and Routing: 0.35 um CMOS 18'th order half-band FIR filter

layout, a subsytem for a switched capacitor mixed signal sonar

device. The advantage to this design is that every other

coefficient is zero, and non-zero coefficients are symmetrical, so the

ROM storage is reduced significantly.